-利用新颖的分离闸极技术提高位元密度–

东京--(美国商业资讯)--鎧侠株式会社(Kioxia Corporation)今日宣布将使用专门设计的半圆形浮动闸极(FG)单元开发全球第一个[1]叁维(3D)半圆形分离闸极型快闪记忆体单元结构Twin BiCS FLASH。与传统的圆形电荷陷阱(CT)单元相比,Twin BiCS FLASH可在更小的单元尺寸下实现出色的程式斜率和更大的程式/擦窗。这些特性使这种新的单元设计成为超过每单元四位元(QLC)的有力候选方案,以显着提高记忆体密度和减少堆叠层。这项技术是於12月11日在加州旧金山举行的IEEE国际电子元件会议(IEDM)上宣布的。

此新闻稿包含多媒体內容。完整新闻稿可在以下网址查阅:https://www.businesswire.com/news/home/20191211006038/en/

3D快闪记忆体技术已透过增加单元堆叠层的数量以及实现多层堆叠沉积和高深宽比蚀刻,以每位元低成本实现高位元密度。近年来,随着单元层的数量超过100,在蚀刻剖面控制、尺寸均匀性和生产率之间控制权衡取捨变得越来越具有挑战性。为克服这一问题,鎧侠透过在传统圆形单元中分裂闸极以减小单元尺寸(与传统圆形单元相比),开发了一种新的半圆形单元设计,从而可以在较少数量的单元层上实现更高密度的记忆体。

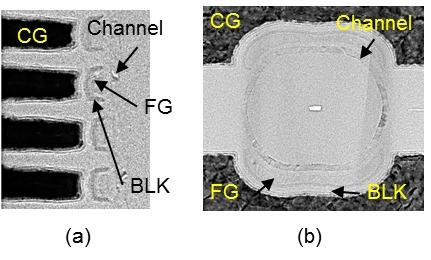

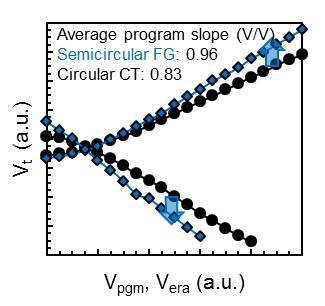

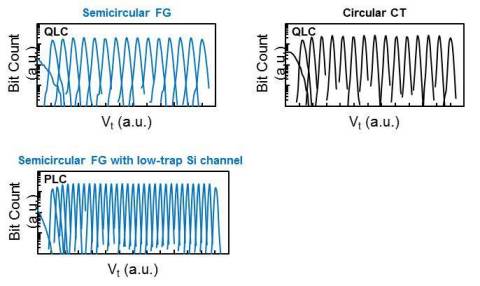

归功於曲率效应,圆形控制闸极提供大於平面闸极的程式视窗,且减少饱和问题,在曲率效应中,透过穿隧介电层的载流子注入得以增强,同时减少了区块(BLK)介电层的电子洩漏。在这种分离闸极型单元设计中,圆形控制闸被对称地分为两个半圆形门,以利用程式/擦除动力学的大幅改进。如图1所示,导电储存层与高k BLK介电层结合,用以提高电荷捕获效率,实现高耦合比,以获取程式视窗并减少电子从FG洩漏,从而缓解饱和问题。图2中的实验程式/擦除特性表明,具有基於高-k的 BLK的半圆形FG单元在较大的圆形CT单元上的程式斜率和程式/擦窗中显示增益显着。具有卓越的程式/擦除特性的半圆形FG单元可望在较小的单元尺寸下获得相对紧密的QLC Vt分布。此外,低陷阱Si通道的整合使每个单元可以具有四个以上的位元,例如,如图3所示的五层单元(PLC)。这些结果证实,半圆形FG单元是追求更高位元密度的可行方案。

展望未来,鎧侠致力於快闪记忆体创新的研发工作将包括继续进行Twin BiCS FLASH开发,并寻求其实际应用。IEDM 2019期间,Kioxia还发表了其他六篇论文,重点介绍该公司在快闪记忆体领域的密集研发活动。

[1] 来源:鎧侠株式会社,截至2019年12月12日。

关於鎧侠

鎧侠是全球记忆体解决方案领导者,致力於开发、生产和销售快闪记忆体及固态硬碟(SSD)。东芝公司於1987年发明了NAND快闪记忆体,2017年4月,鎧侠前身东芝记忆体集团从东芝公司分割。鎧侠致力於以记忆体来提升世界,提供的产品、服务和系统可为客户创造选择,同时为社会创造记忆体的价值。鎧侠创新的3D快闪记忆体技术BiCS FLASH™,正在塑造诸多高密度应用的未来储存方式,其中包括先进智慧手机、PC、SSD、汽车和资料中心等。

原文版本可在businesswire.com上查阅:https://www.businesswire.com/news/home/20191211006038/en/

免责声明:本公告之原文版本乃官方授权版本。译文仅供方便瞭解之用,烦请参照原文,原文版本乃唯一具法律效力之版本。

联络方式:

鎧侠控股株式会社

Kota Yamaji

公共关係

电话:+81-3-6478-2319

kioxia-hd-pr@kioxia.com

製成的半圆形FG单元(a)剖面图(b)平面图(图片:美国商业资讯)

半圆形FG单元和圆形CT单元在实验程式/擦除特性方面的比较(图片:美国商业资讯)

使用校正参数进行程式设计后的模拟Vt分布(图片:美国商业资讯)

财华网所刊载内容之知识产权为财华网及相关权利人专属所有或持有。未经许可,禁止进行转载、摘编、复制及建立镜像等任何使用。

如有意愿转载,请发邮件至content@finet.com.hk,获得书面确认及授权后,方可转载。

更多精彩内容,请登陆

财华香港网(https://www.finet.hk/)

财华智库网(https://www.finet.com.cn)

现代电视(http://www.fintv.hk)